Part I

Chapter 1 – The Best Optimizer Is between Your Ears

The Human Element of Code Optimization

This book is devoted to a topic near and dear to my heart: writing software that pushes PCs to the limit. Given run-of-the-mill software, PCs run like the 97-pound-weakling minicomputers they are. Give them the proper care, however, and those ugly boxes are capable of miracles. The key is this: Only on microcomputers do you have the run of the whole machine, without layers of operating systems, drivers, and the like getting in the way. You can do anything you want, and you can understand everything that’s going on, if you so wish.

As we’ll see shortly, you should indeed so wish.

Is performance still an issue in this era of cheap 486 computers and super-fast Pentium computers? You bet. How many programs that you use really run so fast that you wouldn’t be happier if they ran faster? We’re so used to slow software that when a compile-and-link sequence that took two minutes on a PC takes just ten seconds on a 486 computer, we’re ecstatic—when in truth we should be settling for nothing less than instantaneous response.

Impossible, you say? Not with the proper design, including incremental compilation and linking, use of extended and/or expanded memory, and well-crafted code. PCs can do just about anything you can imagine (with a few obvious exceptions, such as applications involving super-computer-class number-crunching) if you believe that it can be done, if you understand the computer inside and out, and if you’re willing to think past the obvious solution to unconventional but potentially more fruitful approaches.

My point is simply this: PCs can work wonders. It’s not easy coaxing them into doing that, but it’s rewarding—and it’s sure as heck fun. In this book, we’re going to work some of those wonders, starting…

…now.

Understanding High Performance

Before we can create high-performance code, we must understand what high performance is. The objective (not always attained) in creating high-performance software is to make the software able to carry out its appointed tasks so rapidly that it responds instantaneously, as far as the user is concerned. In other words, high-performance code should ideally run so fast that any further improvement in the code would be pointless.

Notice that the above definition most emphatically does not say anything about making the software as fast as possible. It also does not say anything about using assembly language, or an optimizing compiler, or, for that matter, a compiler at all. It also doesn’t say anything about how the code was designed and written. What it does say is that high-performance code shouldn’t get in the user’s way—and that’s all.

That’s an important distinction, because all too many programmers think that assembly language, or the right compiler, or a particular high-level language, or a certain design approach is the answer to creating high-performance code. They’re not, any more than choosing a certain set of tools is the key to building a house. You do indeed need tools to build a house, but any of many sets of tools will do. You also need a blueprint, an understanding of everything that goes into a house, and the ability to use the tools.

Likewise, high-performance programming requires a clear understanding of the purpose of the software being built, an overall program design, algorithms for implementing particular tasks, an understanding of what the computer can do and of what all relevant software is doing—and solid programming skills, preferably using an optimizing compiler or assembly language. The optimization at the end is just the finishing touch, however.

Without good design, good algorithms, and complete understanding of the program’s operation, your carefully optimized code will amount to one of mankind’s least fruitful creations—a fast slow program.

“What’s a fast slow program?” you ask. That’s a good question, and a brief (true) story is perhaps the best answer.

When Fast Isn’t Fast

In the early 1970s, as the first hand-held calculators were hitting the market, I knew a fellow named Irwin. He was a good student, and was planning to be an engineer. Being an engineer back then meant knowing how to use a slide rule, and Irwin could jockey a slipstick with the best of them. In fact, he was so good that he challenged a fellow with a calculator to a duel—and won, becoming a local legend in the process.

When you get right down to it, though, Irwin was spitting into the wind. In a few short years his hard-earned slipstick skills would be worthless, and the entire discipline would be essentially wiped from the face of the earth. What’s more, anyone with half a brain could see that changeover coming. Irwin had basically wasted the considerable effort and time he had spent optimizing his soon-to-be-obsolete skills.

What does all this have to do with programming? Plenty. When you spend time optimizing poorly-designed assembly code, or when you count on an optimizing compiler to make your code fast, you’re wasting the optimization, much as Irwin did. Particularly in assembly, you’ll find that without proper up-front design and everything else that goes into high-performance design, you’ll waste considerable effort and time on making an inherently slow program as fast as possible—which is still slow—when you could easily have improved performance a great deal more with just a little thought. As we’ll see, handcrafted assembly language and optimizing compilers matter, but less than you might think, in the grand scheme of things—and they scarcely matter at all unless they’re used in the context of a good design and a thorough understanding of both the task at hand and the PC.

Rules for Building High-Performance Code

We’ve got the following rules for creating high-performance software:

- Know where you’re going (understand the objective of the software).

- Make a big map (have an overall program design firmly in mind, so the various parts of the program and the data structures work well together).

- Make lots of little maps (design an algorithm for each separate part of the overall design).

- Know the territory (understand exactly how the computer carries out each task).

- Know when it matters (identify the portions of your programs where performance matters, and don’t waste your time optimizing the rest).

- Always consider the alternatives (don’t get stuck on a single approach; odds are there’s a better way, if you’re clever and inventive enough).

- Know how to turn on the juice (optimize the code as best you know how when it does matter).

Making rules is easy; the hard part is figuring out how to apply them in the real world. For my money, examining some actual working code is always a good way to get a handle on programming concepts, so let’s look at some of the performance rules in action.

Know Where You’re Going

If we’re going to create high-performance code, first we have to know what that code is going to do. As an example, let’s write a program that generates a 16-bit checksum of the bytes in a file. In other words, the program will add each byte in a specified file in turn into a 16-bit value. This checksum value might be used to make sure that a file hasn’t been corrupted, as might occur during transmission over a modem or if a Trojan horse virus rears its ugly head. We’re not going to do anything with the checksum value other than print it out, however; right now we’re only interested in generating that checksum value as rapidly as possible.

Make a Big Map

How are we going to generate a checksum value for a specified file? The logical approach is to get the file name, open the file, read the bytes out of the file, add them together, and print the result. Most of those actions are straightforward; the only tricky part lies in reading the bytes and adding them together.

Make Lots of Little Maps

Actually, we’re only going to make one little map, because we only have one program section that requires much thought—the section that reads the bytes and adds them up. What’s the best way to do this?

It would be convenient to load the entire file into memory and then sum the bytes in one loop. Unfortunately, there’s no guarantee that any particular file will fit in the available memory; in fact, it’s a sure thing that many files won’t fit into memory, so that approach is out.

Well, if the whole file won’t fit into memory, one byte surely will. If we read the file one byte at a time, adding each byte to the checksum value before reading the next byte, we’ll minimize memory requirements and be able to handle any size file at all.

Sounds good, eh? Listing 1.1 shows an implementation of this

approach. Listing 1.1 uses C’s read() function to read a

single byte, adds the byte into the checksum value, and loops back to

handle the next byte until the end of the file is reached. The code is

compact, easy to write, and functions perfectly—with one slight

hitch:

It’s slow.

LISTING 1.1 L1-1.C

/*

* Program to calculate the 16-bit checksum of all bytes in the

* specified file. Obtains the bytes one at a time via read(),

* letting DOS perform all data buffering.

*/

#include <stdio.h>

#include <fcntl.h>

main(int argc, char *argv[]) {

int Handle;

unsigned char Byte;

unsigned int Checksum;

int ReadLength;

if ( argc != 2 ) {

printf("usage: checksum filename\n");

exit(1);

}

if ( (Handle = open(argv[1], O_RDONLY | O_BINARY)) == -1 ) {

printf("Can't open file: %s\n", argv[1]);

exit(1);

}

/* Initialize the checksum accumulator */

Checksum = 0;

/* Add each byte in turn into the checksum accumulator */

while ( (ReadLength = read(Handle, &Byte, sizeof(Byte))) > 0 ) {

Checksum += (unsigned int) Byte;

}

if ( ReadLength == -1 ) {

printf("Error reading file %s\n", argv[1]);

exit(1);

}

/* Report the result */

printf("The checksum is: %u\n", Checksum);

exit(0);

}Table 1.1 shows the time taken for Listing 1.1 to generate a checksum of the WordPerfect version 4.2 thesaurus file, TH.WP (362,293 bytes in size), on a 10 MHz AT machine of no special parentage. Execution times are given for Listing 1.1 compiled with Borland and Microsoft compilers, with optimization both on and off; all four times are pretty much the same, however, and all are much too slow to be acceptable. Listing 1.1 requires over two and one-half minutes to checksum one file!

Listings 1.2 and 1.3 form the C/assembly equivalent to Listing 1.1, and Listings 1.6 and 1.7 form the C/assembly equivalent to Listing 1.5.

These results make it clear that it’s folly to rely on your compiler’s optimization to make your programs fast. Listing 1.1 is simply poorly designed, and no amount of compiler optimization will compensate for that failing. To drive home the point, Listings 1.2 and 1.3, which together are equivalent to Listing 1.1 except that the entire checksum loop is written in tight assembly code. The assembly language implementation is indeed faster than any of the C versions, as shown in Table 1.1, but it’s less than 10 percent faster, and it’s still unacceptably slow.

| Listing | Borland | Microsoft | Borland | Microsoft | Assembly | Optimization Ratio |

|---|---|---|---|---|---|---|

| (no opt) | (no opt) | (opt) | (opt) | |||

| 1 | 166.9 | 166.8 | 167.0 | 165.8 | 155.1 | 1.08 |

| 4 | 13.5 | 13.6 | 13.5 | 13.5 | … | 1.01 |

| 5 | 4.7 | 5.5 | 3.8 | 3.4 | 2.7 | 2.04 |

| Ratio best designed to worst designed | 35.51 | 30.33 | 43.95 | 48.76 | 57.44 |

Note: The execution times (in seconds) for this chapter’s listings were timed when the compiled listings were run on the WordPerfect 4.2 thesaurus file TH.WP (362,293 bytes in size), as compiled in the small model with Borland and Microsoft compilers with optimization on (opt) and off (no opt). All times were measured with Paradigm Systems’ TIMER program on a 10 MHz 1-wait-state AT clone with a 28-ms hard disk, with disk caching turned off.

LISTING 1.2 L1-2.C

/*

* Program to calculate the 16-bit checksum of the stream of bytes

* from the specified file. Obtains the bytes one at a time in

* assembler, via direct calls to DOS.

*/

#include <stdio.h>

#include <fcntl.h>

main(int argc, char *argv[]) {

int Handle;

unsigned char Byte;

unsigned int Checksum;

int ReadLength;

if ( argc != 2 ) {

printf("usage: checksum filename\n");

exit(1);

}

if ( (Handle = open(argv[1], O_RDONLY | O_BINARY)) == -1 ) {

printf("Can't open file: %s\n", argv[1]);

exit(1);

}

if ( !ChecksumFile(Handle, &Checksum) ) {

printf("Error reading file %s\n", argv[1]);

exit(1);

}

/* Report the result */

printf("The checksum is: %u\n", Checksum);

exit(0);

}LISTING 1.3 L1-3.ASM

; Assembler subroutine to perform a 16-bit checksum on the file

; opened on the passed-in handle. Stores the result in the

; passed-in checksum variable. Returns 1 for success, 0 for error.

;

; Call as:

; int ChecksumFile(unsigned int Handle, unsigned int *Checksum);

;

; where:

; Handle = handle # under which file to checksum is open

; Checksum = pointer to unsigned int variable checksum is

; to be stored in

;

; Parameter structure:

;

Parms struc

dw ? ;pushed BP

dw ? ;return address

Handle dw ?

Checksum dw ?

Parms ends

;

.model small

.data

TempWord label word

TempByte db ? ;each byte read by DOS will be stored here

db 0 ;high byte of TempWord is always 0

;for 16-bit adds

;

.code

public _ChecksumFile

_ChecksumFile proc near

push bp

mov bp,sp

push si ;save C's register variable

;

mov bx,[bp+Handle] ;get file handle

sub si,si ;zero the checksum ;accumulator

mov cx,1 ;request one byte on each ;read

mov dx,offset TempByte ;point DX to the byte in

;which DOS should store

;each byte read

ChecksumLoop:

mov ah,3fh ;DOS read file function #

int 21h ;read the byte

jc ErrorEnd ;an error occurred

and ax,ax ;any bytes read?

jz Success ;no-end of file reached-we're done

add si,[TempWord] ;add the byte into the

;checksum total

jmp ChecksumLoop

ErrorEnd:

sub ax,ax ;error

jmp short Done

Success:

mov bx,[bp+Checksum] ;point to the checksum variable

mov [bx],si ;save the new checksum

mov ax,1 ;success

;

Done:

pop si ;restore C's register variable

pop bp

ret

_ChecksumFile endp

endThe lesson is clear: Optimization makes code faster, but without proper design, optimization just creates fast slow code.

Well, then, how are we going to improve our design? Before we can do that, we have to understand what’s wrong with the current design.

Know the Territory

Just why is Listing 1.1 so slow? In a word: overhead. The C library

implements the read() function by calling DOS to read the

desired number of bytes. (I figured this out by watching the code

execute with a debugger, but you can buy library source code from both

Microsoft and Borland.) That means that Listing 1.1 (and Listing 1.3 as

well) executes one DOS function per byte processed—and DOS functions,

especially this one, come with a lot of overhead.

For starters, DOS functions are invoked with interrupts, and

interrupts are among the slowest instructions of the x86 family CPUs.

Then, DOS has to set up internally and branch to the desired function,

expending more cycles in the process. Finally, DOS has to search its own

buffers to see if the desired byte has already been read, read it from

the disk if not, store the byte in the specified location, and return.

All of that takes a long time—far, far longer than the rest of

the main loop in Listing 1.1. In short, Listing 1.1 spends virtually all

of its time executing read(), and most of that time is

spent somewhere down in DOS.

You can verify this for yourself by watching the code with a debugger or using a code profiler, but take my word for it: There’s a great deal of overhead to DOS calls, and that’s what’s draining the life out of Listing 1.1.

How can we speed up Listing 1.1? It should be clear that we must somehow avoid invoking DOS for every byte in the file, and that means reading more than one byte at a time, then buffering the data and parceling it out for examination one byte at a time. By gosh, that’s a description of C’s stream I/O feature, whereby C reads files in chunks and buffers the bytes internally, doling them out to the application as needed by reading them from memory rather than calling DOS. Let’s try using stream I/O and see what happens.

Listing 1.4 is similar to Listing 1.1, but uses fopen()

and getc() (rather than open() and

read()) to access the file being checksummed. The results

confirm our theories splendidly, and validate our new design. As shown

in Table 1.1, Listing 1.4 runs more than an order of magnitude faster

than even the assembly version of Listing 1.1, even though Listing

1.1 and Listing 1.4 look almost the same. To the casual observer,

read() and getc() would seem slightly

different but pretty much interchangeable, and yet in this application

the performance difference between the two is about the same as that

between a 4.77 MHz PC and a 16 MHz 386.

Make sure you understand what really goes on when you insert a seemingly-innocuous function call into the time-critical portions of your code.

In this case that means knowing how DOS and the C/C++ file-access libraries do their work. In other words, know the territory!

LISTING 1.4 L1-4.C

/*

* Program to calculate the 16-bit checksum of the stream of bytes

* from the specified file. Obtains the bytes one at a time via

* getc(), allowing C to perform data buffering.

*/

#include <stdio.h>

main(int argc, char *argv[]) {

FILE *CheckFile;

int Byte;

unsigned int Checksum;

if ( argc != 2 ) {

printf("usage: checksum filename\n");

exit(1);

}

if ( (CheckFile = fopen(argv[1], "rb")) == NULL ) {

printf("Can't open file: %s\n", argv[1]);

exit(1);

}

/* Initialize the checksum accumulator */

Checksum = 0;

/* Add each byte in turn into the checksum accumulator */

while ( (Byte = getc(CheckFile)) != EOF ) {

Checksum += (unsigned int) Byte;

}

/* Report the result */

printf("The checksum is: %u\n", Checksum);

exit(0);

}Know When It Matters

The last section contained a particularly interesting phrase: the time-critical portions of your code. Time-critical portions of your code are those portions in which the speed of the code makes a significant difference in the overall performance of your program—and by “significant,” I don’t mean that it makes the code 100 percent faster, or 200 percent, or any particular amount at all, but rather that it makes the program more responsive and/or usable from the user’s perspective.

Don’t waste time optimizing non-time-critical code: set-up code, initialization code, and the like. Spend your time improving the performance of the code inside heavily-used loops and in the portions of your programs that directly affect response time. Notice, for example, that I haven’t bothered to implement a version of the checksum program entirely in assembly; Listings 1.2 and 1.6 call assembly subroutines that handle the time-critical operations, but C is still used for checking command-line parameters, opening files, printing, and the like.

If you were to implement any of the listings in this chapter entirely in hand-optimized assembly, I suppose you might get a performance improvement of a few percent—but I rather doubt you’d get even that much, and you’d sure as heck spend an awful lot of time for whatever meager improvement does result. Let C do what it does well, and use assembly only when it makes a perceptible difference.

Besides, we don’t want to optimize until the design is refined to our satisfaction, and that won’t be the case until we’ve thought about other approaches.

Always Consider the Alternatives

Listing 1.4 is good, but let’s see if there are other—perhaps less

obvious—ways to get the same results faster. Let’s start by considering

why Listing 1.4 is so much better than Listing 1.1. Like

read(), getc() calls DOS to read from the

file; the speed improvement of Listing 1.4 over Listing 1.1 occurs

because getc() reads many bytes at once via DOS, then

manages those bytes for us. That’s faster than reading them one at a

time using read()—but there’s no reason to think that it’s

faster than having our program read and manage blocks itself. Easier,

yes, but not faster.

Consider this: Every invocation of getc() involves

pushing a parameter, executing a call to the C library function, getting

the parameter (in the C library code), looking up information about the

desired stream, unbuffering the next byte from the stream, and returning

to the calling code. That takes a considerable amount of time,

especially by contrast with simply maintaining a pointer to a buffer and

whizzing through the data in the buffer inside a single loop.

There are four reasons that many programmers would give for not trying to improve on Listing 1.4:

The code is already fast enough.

The code works, and some people are content with code that works, even when it’s slow enough to be annoying.

The C library is written in optimized assembly, and it’s likely to be faster than any code that the average programmer could write to perform essentially the same function.

The C library conveniently handles the buffering of file data, and it would be a nuisance to have to implement that capability.

I’ll ignore the first reason, both because performance is no longer an issue if the code is fast enough and because the current application does not run fast enough—13 seconds is a long time. (Stop and wait for 13 seconds while you’re doing something intense, and you’ll see just how long it is.)

The second reason is the hallmark of the mediocre programmer. Know when optimization matters—and then optimize when it does!

The third reason is often fallacious. C library functions are not always written in assembly, nor are they always particularly well-optimized. (In fact, they’re often written for portability, which has nothing to do with optimization.) What’s more, they’re general-purpose functions, and often can be outperformed by well-but-not-brilliantly-written code that is well-matched to a specific task. As an example, consider Listing 1.5, which uses internal buffering to handle blocks of bytes at a time. Table 1.1 shows that Listing 1.5 is 2.5 to 4 times faster than Listing 1.4 (and as much as 49 times faster than Listing 1.1!), even though it uses no assembly at all.

Clearly, you can do well by using special-purpose C code in place of a C library function—if you have a thorough understanding of how the C library function operates and exactly what your application needs done. Otherwise, you’ll end up rewriting C library functions in C, which makes no sense at all.

LISTING 1.5 L1-5.C

/*

* Program to calculate the 16-bit checksum of the stream of bytes

* from the specified file. Buffers the bytes internally, rather

* than letting C or DOS do the work.

*/

#include <stdio.h>

#include <fcntl.h>

#include <alloc.h> /* alloc.h for Borland,

malloc.h for Microsoft */

#define BUFFER_SIZE 0x8000 /* 32Kb data buffer */

main(int argc, char *argv[]) {

int Handle;

unsigned int Checksum;

unsigned char *WorkingBuffer, *WorkingPtr;

int WorkingLength, LengthCount;

if ( argc != 2 ) {

printf("usage: checksum filename\n");

exit(1);

}

if ( (Handle = open(argv[1], O_RDONLY | O_BINARY)) == -1 ) {

printf("Can't open file: %s\n", argv[1]);

exit(1);

}

/* Get memory in which to buffer the data */

if ( (WorkingBuffer = malloc(BUFFER_SIZE)) == NULL ) {

printf("Can't get enough memory\n");

exit(1);

}

/* Initialize the checksum accumulator */

Checksum = 0;

/* Process the file in BUFFER_SIZE chunks */

do {

if ( (WorkingLength = read(Handle, WorkingBuffer,

BUFFER_SIZE)) == -1 ) {

printf("Error reading file %s\n", argv[1]);

exit(1);

}

/* Checksum this chunk */

WorkingPtr = WorkingBuffer;

LengthCount = WorkingLength;

while ( LengthCount-- ) {

/* Add each byte in turn into the checksum accumulator */

Checksum += (unsigned int) *WorkingPtr++;

}

} while ( WorkingLength );

/* Report the result */

printf("The checksum is: %u\n", Checksum);

exit(0);

}That brings us to the fourth reason: avoiding an internal-buffered implementation like Listing 1.5 because of the difficulty of coding such an approach. True, it is easier to let a C library function do the work, but it’s not all that hard to do the buffering internally. The key is the concept of handling data in restartable blocks; that is, reading a chunk of data, operating on the data until it runs out, suspending the operation while more data is read in, and then continuing as though nothing had happened.

In Listing 1.5 the restartable block implementation is pretty simple because checksumming works with one byte at a time, forgetting about each byte immediately after adding it into the total. Listing 1.5 reads in a block of bytes from the file, checksums the bytes in the block, and gets another block, repeating the process until the entire file has been processed. In Chapter 5, we’ll see a more complex restartable block implementation, involving searching for text strings.

At any rate, Listing 1.5 isn’t much more complicated than Listing 1.4—and it’s a lot faster. Always consider the alternatives; a bit of clever thinking and program redesign can go a long way.

Know How to Turn On the Juice

I have said time and again that optimization is pointless until the design is settled. When that time comes, however, optimization can indeed make a significant difference. Table 1.1 indicates that the optimized version of Listing 1.5 produced by Microsoft C outperforms an unoptimized version of the same code by more than 60 percent. What’s more, a mostly-assembly version of Listing 1.5, shown in Listings 1.6 and 1.7, outperforms even the best-optimized C version of Listing 1.5 by 26 percent. These are considerable improvements, well worth pursuing—once the design has been maxed out.

LISTING 1.6 L1-6.C

/*

* Program to calculate the 16-bit checksum of the stream of bytes

* from the specified file. Buffers the bytes internally, rather

* than letting C or DOS do the work, with the time-critical

* portion of the code written in optimized assembler.

*/

#include <stdio.h>

#include <fcntl.h>

#include <alloc.h> /* alloc.h for Borland,

malloc.h for Microsoft */

#define BUFFER_SIZE 0x8000 /* 32K data buffer */

main(int argc, char *argv[]) {

int Handle;

unsigned int Checksum;

unsigned char *WorkingBuffer;

int WorkingLength;

if ( argc != 2 ) {

printf("usage: checksum filename\n");

exit(1);

}

if ( (Handle = open(argv[1], O_RDONLY | O_BINARY)) == -1 ) {

printf("Can't open file: %s\n", argv[1]);

exit(1);

}

/* Get memory in which to buffer the data */

if ( (WorkingBuffer = malloc(BUFFER_SIZE)) == NULL ) {

printf("Can't get enough memory\n");

exit(1);

}

/* Initialize the checksum accumulator */

Checksum = 0;

/* Process the file in 32K chunks */

do {

if ( (WorkingLength = read(Handle, WorkingBuffer,

BUFFER_SIZE)) == -1 ) {

printf("Error reading file %s\n", argv[1]);

exit(1);

}

/* Checksum this chunk if there's anything in it */

if ( WorkingLength )

ChecksumChunk(WorkingBuffer, WorkingLength, &Checksum);

} while ( WorkingLength );

/* Report the result */

printf("The checksum is: %u\n", Checksum);

exit(0);

}LISTING 1.7 L1-7.ASM

; Assembler subroutine to perform a 16-bit checksum on a block of

; bytes 1 to 64K in size. Adds checksum for block into passed-in

; checksum.

;

; Call as:

; void ChecksumChunk(unsigned char *Buffer,

; unsigned int BufferLength, unsigned int *Checksum);

;

; where:

; Buffer = pointer to start of block of bytes to checksum

; BufferLength = # of bytes to checksum (0 means 64K, not 0)

; Checksum = pointer to unsigned int variable checksum is

;stored in

;

; Parameter structure:

;

Parms struc

dw ? ;pushed BP

dw ? ;return address

Buffer dw ?

BufferLength dw ?

Checksum dw ?

Parms ends

;

.model small

.code

public _ChecksumChunk

_ChecksumChunk proc near

push bp

mov bp,sp

push si ;save C's register variable

;

cld ;make LODSB increment SI

mov si,[bp+Buffer] ;point to buffer

mov cx,[bp+BufferLength] ;get buffer length

mov bx,[bp+Checksum] ;point to checksum variable

mov dx,[bx] ;get the current checksum

sub ah,ah ;so AX will be a 16-bit value after LODSB

ChecksumLoop:

lodsb ;get the next byte

add dx,ax ;add it into the checksum total

loop ChecksumLoop ;continue for all bytes in block

mov [bx],dx ;save the new checksum

;

pop si ;restore C's register variable

pop bp

ret

_ChecksumChunk endp

endNote that in Table 1.1, optimization makes little difference except in the case of Listing 1.5, where the design has been refined considerably. Execution time in the other cases is dominated by time spent in DOS and/or the C library, so optimization of the code you write is pretty much irrelevant. What’s more, while the approximately two-times improvement we got by optimizing is not to be sneezed at, it pales against the up-to-50-times improvement we got by redesigning.

By the way, the execution times even of Listings 1.6 and 1.7 are dominated by DOS disk access times. If a disk cache is enabled and the file to be checksummed is already in the cache, the assembly version is three times as fast as the C version. In other words, the inherent nature of this application limits the performance improvement that can be obtained via assembly. In applications that are more CPU-intensive and less disk-bound, particularly those applications in which string instructions and/or unrolled loops can be used effectively, assembly tends to be considerably faster relative to C than it is in this very specific case.

Don’t get hung up on optimizing compilers or assembly language—the best optimizer is between your ears.

All this is basically a way of saying: Know where you’re going, know the territory, and know when it matters.

Where We’ve Been, What We’ve Seen

What have we learned? Don’t let other people’s code—even DOS—do the work for you when speed matters, at least not without knowing what that code does and how well it performs.

Optimization only matters after you’ve done your part on the program design end. Consider the ratios on the vertical axis of Table 1.1, which show that optimization is almost totally wasted in the checksumming application without an efficient design. Optimization is no panacea. Table 1.1 shows a two-times improvement from optimization—and a 50-times-plus improvement from redesign. The longstanding debate about which C compiler optimizes code best doesn’t matter quite so much in light of Table 1.1, does it? Your organic optimizer matters much more than your compiler’s optimizer, and there’s always assembly for those usually small sections of code where performance really matters.

Where We’re Going

This chapter has presented a quick step-by-step overview of the design process. I’m not claiming that this is the only way to create high-performance code; it’s just an approach that works for me. Create code however you want, but never forget that design matters more than detailed optimization. Never stop looking for inventive ways to boost performance—and never waste time speeding up code that doesn’t need to be sped up.

I’m going to focus on specific ways to create high-performance code from now on. In Chapter 5, we’ll continue to look at restartable blocks and internal buffering, in the form of a program that searches files for text strings.

Chapter 2 – A World Apart

The Unique Nature of Assembly Language Optimization

As I showed in the previous chapter, optimization is by no means always a matter of “dropping into assembly.” In fact, in performance tuning high-level language code, assembly should be used rarely, and then only after you’ve made sure a badly chosen or clumsily implemented algorithm isn’t eating you alive. Certainly if you use assembly at all, make absolutely sure you use it right. The potential of assembly code to run slowly is poorly understood by a lot of people, but that potential is great, especially in the hands of the ignorant.

Truly great optimization, however, happens only at the assembly level, and it happens in response to a set of dynamics that is totally different from that governing C/C++ or Pascal optimization. I’ll be speaking of assembly-level optimization time and again in this book, but when I do, I think it will be helpful if you have a grasp of those assembly specific dynamics.

As usual, the best way to wade in is to present a real-world example.

Instructions: The Individual versus the Collective

Some time ago, I was asked to work over a critical assembly subroutine in order to make it run as fast as possible. The task of the subroutine was to construct a nibble out of four bits read from different bytes, rotating and combining the bits so that they ultimately ended up neatly aligned in bits 3-0 of a single byte. (In case you’re curious, the object was to construct a 16-color pixel from bits scattered over 4 bytes.) I examined the subroutine line by line, saving a cycle here and a cycle there, until the code truly seemed to be optimized. When I was done, the key part of the code looked something like this:

LoopTop:

lodsb ;get the next byte to extract a bit from

and al,ah ;isolate the bit we want

rol al,cl ;rotate the bit into the desired position

or bl,al ;insert the bit into the final nibble

dec cx ;the next bit goes 1 place to the right

dec dx ;count down the number of bits

jnz LoopTop ;process the next bit, if anyNow, it’s hard to write code that’s much faster than seven instructions, only one of which accesses memory, and most programmers would have called it a day at this point. Still, something bothered me, so I spent a bit of time going over the code again. Suddenly, the answer struck me—the code was rotating each bit into place separately, so that a multibit rotation was being performed every time through the loop, for a total of four separate time-consuming multibit rotations!

While the instructions themselves were individually optimized, the overall approach did not make the best possible use of the instructions.

I changed the code to the following:

LoopTop:

lodsb ;get the next byte to extract a bit from

and al,ah ;isolate the bit we want

or bl,al ;insert the bit into the final nibble

rol bl,1 ;make room for the next bit

dec dx ;count down the number of bits

jnz LoopTop ;process the next bit, if any

rol bl,cl ;rotate all four bits into their final

; positions at the same timeThis moved the costly multibit rotation out of the loop so that it

was performed just once, rather than four times. While the code may not

look much different from the original, and in fact still contains

exactly the same number of instructions, the performance of the entire

subroutine improved by about 10 percent from just this one change.

(Incidentally, that wasn’t the end of the optimization; I eliminated the

DEC and JNZ instructions by expanding the four

iterations of the loop—but that’s a tale for another chapter.)

The point is this: To write truly superior assembly programs, you need to know what the various instructions do and which instructions execute fastest…and more. You must also learn to look at your programming problems from a variety of perspectives so that you can put those fast instructions to work in the most effective ways.

Assembly Is Fundamentally Different

Is it really so hard as all that to write good assembly code for the PC? Yes! Thanks to the decidedly quirky nature of the x86 family CPUs, assembly language differs fundamentally from other languages, and is undeniably harder to work with. On the other hand, the potential of assembly code is much greater than that of other languages, as well.

To understand why this is so, consider how a program gets written. A programmer examines the requirements of an application, designs a solution at some level of abstraction, and then makes that design come alive in a code implementation. If not handled properly, the transformation that takes place between conception and implementation can reduce performance tremendously; for example, a programmer who implements a routine to search a list of 100,000 sorted items with a linear rather than binary search will end up with a disappointingly slow program.

Transformation Inefficiencies

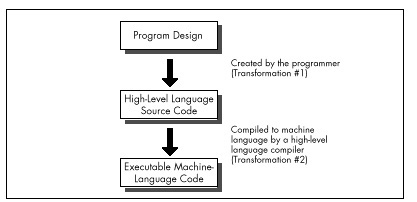

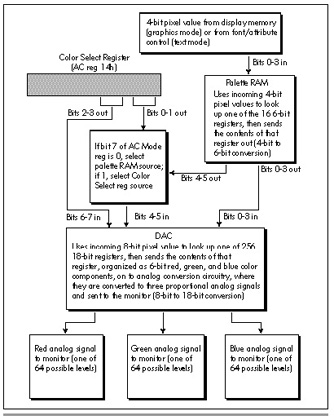

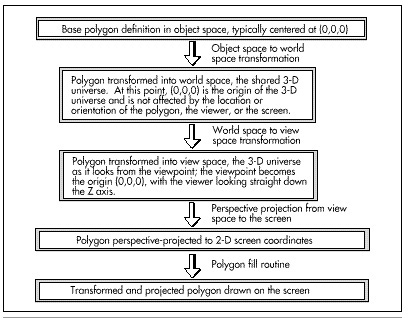

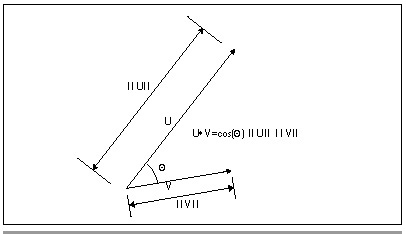

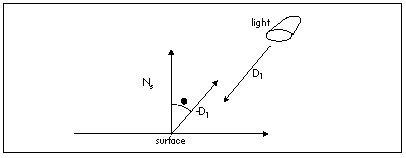

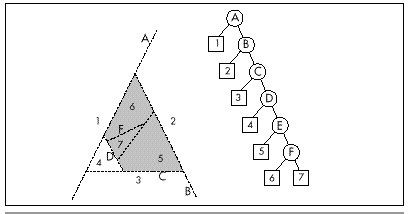

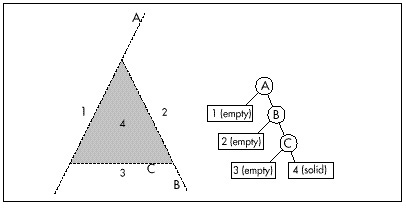

No matter how well an implementation is derived from the corresponding design, however, high-level languages like C/C++ and Pascal inevitably introduce additional transformation inefficiencies, as shown in Figure 2.1.

The process of turning a design into executable code by way of a high-level language involves two transformations: one performed by the programmer to generate source code, and another performed by the compiler to turn source code into machine language instructions. Consequently, the machine language code generated by compilers is usually less than optimal given the requirements of the original design.

High-level languages provide artificial environments that lend themselves relatively well to human programming skills, in order to ease the transition from design to implementation. The price for this ease of implementation is a considerable loss of efficiency in transforming source code into machine language. This is particularly true given that the x86 family in real and 16-bit protected mode, with its specialized memory-addressing instructions and segmented memory architecture, does not lend itself particularly well to compiler design. Even the 32-bit mode of the 386 and its successors, with their more powerful addressing modes, offer fewer registers than compilers would like.

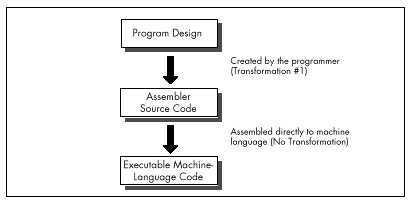

Assembly, on the other hand, is simply a human-oriented representation of machine language. As a result, assembly provides a difficult programming environment—the bare hardware and systems software of the computer—but properly constructed assembly programs suffer no transformation loss, as shown in Figure 2.2.

Only one transformation is required when creating an assembler program, and that single transformation is completely under the programmer’s control. Assemblers perform no transformation from source code to machine language; instead, they merely map assembler instructions to machine language instructions on a one-to-one basis. As a result, the programmer is able to produce machine language code that’s precisely tailored to the needs of each task a given application requires.

The key, of course, is the programmer, since in assembly the programmer must essentially perform the transformation from the application specification to machine language entirely on his or her own. (The assembler merely handles the direct translation from assembly to machine language.)

Self-Reliance

The first part of assembly language optimization, then, is self. An assembler is nothing more than a tool to let you design machine-language programs without having to think in hexadecimal codes. So assembly language programmers—unlike all other programmers—must take full responsibility for the quality of their code. Since assemblers provide little help at any level higher than the generation of machine language, the assembly programmer must be capable both of coding any programming construct directly and of controlling the PC at the lowest practical level—the operating system, the BIOS, even the hardware where necessary. High-level languages handle most of this transparently to the programmer, but in assembly everything is fair—and necessary—game, which brings us to another aspect of assembly optimization: knowledge.

Knowledge

In the PC world, you can never have enough knowledge, and every item you add to your store will make your programs better. Thorough familiarity with both the operating system APIs and BIOS interfaces is important; since those interfaces are well-documented and reasonably straightforward, my advice is to get a good book or two and bring yourself up to speed. Similarly, familiarity with the PC hardware is required. While that topic covers a lot of ground—display adapters, keyboards, serial ports, printer ports, timer and DMA channels, memory organization, and more—most of the hardware is well-documented, and articles about programming major hardware components appear frequently in the literature, so this sort of knowledge can be acquired readily enough.

The single most critical aspect of the hardware, and the one about which it is hardest to learn, is the CPU. The x86 family CPUs have a complex, irregular instruction set, and, unlike most processors, they are neither straightforward nor well-documented true code performance. What’s more, assembly is so difficult to learn that most articles and books that present assembly code settle for code that just works, rather than code that pushes the CPU to its limits. In fact, since most articles and books are written for inexperienced assembly programmers, there is very little information of any sort available about how to generate high-quality assembly code for the x86 family CPUs. As a result, knowledge about programming them effectively is by far the hardest knowledge to gather. A good portion of this book is devoted to seeking out such knowledge.

Be forewarned, though: No matter how much you learn about programming the PC in assembly, there’s always more to discover.

The Flexible Mind

Is the never-ending collection of information all there is to the assembly optimization, then? Hardly. Knowledge is simply a necessary base on which to build. Let’s take a moment to examine the objectives of good assembly programming, and the remainder of the forces that act on assembly optimization will fall into place.

Basically, there are only two possible objectives to high-performance assembly programming: Given the requirements of the application, keep to a minimum either the number of processor cycles the program takes to run, or the number of bytes in the program, or some combination of both. We’ll look at ways to achieve both objectives, but we’ll more often be concerned with saving cycles than saving bytes, for the PC generally offers relatively more memory than it does processing horsepower. In fact, we’ll find that two-to-three times performance improvements over already tight assembly code are often possible if we’re willing to spend additional bytes in order to save cycles. It’s not always desirable to use such techniques to speed up code, due to the heavy memory requirements—but it is almost always possible.

You will notice that my short list of objectives for high-performance assembly programming does not include traditional objectives such as easy maintenance and speed of development. Those are indeed important considerations—to persons and companies that develop and distribute software. People who actually buy software, on the other hand, care only about how well that software performs, not how it was developed nor how it is maintained. These days, developers spend so much time focusing on such admittedly important issues as code maintainability and reusability, source code control, choice of development environment, and the like that they often forget rule #1: From the user’s perspective, performance is fundamental.

Comment your code, design it carefully, and write non-time-critical portions in a high-level language, if you wish—but when you write the portions that interact with the user and/or affect response time, performance must be your paramount objective, and assembly is the path to that goal.

Knowledge of the sort described earlier is absolutely essential to fulfilling either of the objectives of assembly programming. What that knowledge doesn’t do by itself is meet the need to write code that both performs to the requirements of the application at hand and also operates as efficiently as possible in the PC environment. Knowledge makes that possible, but your programming instincts make it happen. And it is that intuitive, on-the-fly integration of a program specification and a sea of facts about the PC that is the heart of the Zen-class assembly optimization.

As with Zen of any sort, mastering that Zen of assembly language is more a matter of learning than of being taught. You will have to find your own path of learning, although I will start you on your way with this book. The subtle facts and examples I provide will help you gain the necessary experience, but you must continue the journey on your own. Each program you create will expand your programming horizons and increase the options available to you in meeting the next challenge. The ability of your mind to find surprising new and better ways to craft superior code from a concept—the flexible mind, if you will—is the linchpin of good assembler code, and you will develop this skill only by doing.

Never underestimate the importance of the flexible mind. Good assembly code is better than good compiled code. Many people would have you believe otherwise, but they’re wrong. That doesn’t mean that high-level languages are useless; far from it. High-level languages are the best choice for the majority of programmers, and for the bulk of the code of most applications. When the best code—the fastest or smallest code possible—is needed, though, assembly is the only way to go.

Simple logic dictates that no compiler can know as much about what a piece of code needs to do or adapt as well to those needs as the person who wrote the code. Given that superior information and adaptability, an assembly language programmer can generate better code than a compiler, all the more so given that compilers are constrained by the limitations of high-level languages and by the process of transformation from high-level to machine language. Consequently, carefully optimized assembly is not just the language of choice but the only choice for the 1 percent to 10 percent of code—usually consisting of small, well-defined subroutines—that determines overall program performance, and it is the only choice for code that must be as compact as possible, as well. In the run-of-the-mill, non-time-critical portions of your programs, it makes no sense to waste time and effort on writing optimized assembly code—concentrate your efforts on loops and the like instead; but in those areas where you need the finest code quality, accept no substitutes.

Note that I said that an assembly programmer can generate better code than a compiler, not will generate better code. While it is true that good assembly code is better than good compiled code, it is also true that bad assembly code is often much worse than bad compiled code; since the assembly programmer has so much control over the program, he or she has virtually unlimited opportunities to waste cycles and bytes. The sword cuts both ways, and good assembly code requires more, not less, forethought and planning than good code written in a high-level language.

The gist of all this is simply that good assembly programming is done in the context of a solid overall framework unique to each program, and the flexible mind is the key to creating that framework and holding it together.

Where to Begin?

To summarize, the skill of assembly language optimization is a combination of knowledge, perspective, and a way of thought that makes possible the genesis of absolutely the fastest or the smallest code. With that in mind, what should the first step be? Development of the flexible mind is an obvious step. Still, the flexible mind is no better than the knowledge at its disposal. The first step in the journey toward mastering optimization at that exalted level, then, would seem to be learning how to learn.

Chapter 3 – Assume Nothing

Understanding and Using the Zen Timer

When you’re pushing the envelope in writing optimized PC code, you’re likely to become more than a little compulsive about finding approaches that let you wring more speed from your computer. In the process, you’re bound to make mistakes, which is fine—as long as you watch for those mistakes and learn from them.

A case in point: A few years back, I came across an article about 8088 assembly language called “Optimizing for Speed.” Now, “optimize” is not a word to be used lightly; Webster’s Ninth New Collegiate Dictionary defines optimize as “to make as perfect, effective, or functional as possible,” which certainly leaves little room for error. The author had, however, chosen a small, well-defined 8088 assembly language routine to refine, consisting of about 30 instructions that did nothing more than expand 8 bits to 16 bits by duplicating each bit.

The author of “Optimizing” had clearly fine-tuned the code with care, examining alternative instruction sequences and adding up cycles until he arrived at an implementation he calculated to be nearly 50 percent faster than the original routine. In short, he had used all the information at his disposal to improve his code, and had, as a result, saved cycles by the bushel. There was, in fact, only one slight problem with the optimized version of the routine….

It ran slower than the original version!

The Costs of Ignorance

As diligent as the author had been, he had nonetheless committed a cardinal sin of x86 assembly language programming: He had assumed that the information available to him was both correct and complete. While the execution times provided by Intel for its processors are indeed correct, they are incomplete; the other—and often more important—part of code performance is instruction fetch time, a topic to which I will return in later chapters.

Had the author taken the time to measure the true performance of his code, he wouldn’t have put his reputation on the line with relatively low-performance code. What’s more, had he actually measured the performance of his code and found it to be unexpectedly slow, curiosity might well have led him to experiment further and thereby add to his store of reliable information about the CPU.

There you have an important tenet of assembly language optimization: After crafting the best code possible, check it in action to see if it’s really doing what you think it is. If it’s not behaving as expected, that’s all to the good, since solving mysteries is the path to knowledge. You’ll learn more in this way, I assure you, than from any manual or book on assembly language.

Assume nothing. I cannot emphasize this strongly enough—when you care about performance, do your best to improve the code and then measure the improvement. If you don’t measure performance, you’re just guessing, and if you’re guessing, you’re not very likely to write top-notch code.

Ignorance about true performance can be costly. When I wrote video games for a living, I spent days at a time trying to wring more performance from my graphics drivers. I rewrote whole sections of code just to save a few cycles, juggled registers, and relied heavily on blurry-fast register-to-register shifts and adds. As I was writing my last game, I discovered that the program ran perceptibly faster if I used look-up tables instead of shifts and adds for my calculations. It shouldn’t have run faster, according to my cycle counting, but it did. In truth, instruction fetching was rearing its head again, as it often does, and the fetching of the shifts and adds was taking as much as four times the nominal execution time of those instructions.

Ignorance can also be responsible for considerable wasted effort. I recall a debate in the letters column of one computer magazine about exactly how quickly text can be drawn on a Color/Graphics Adapter (CGA) screen without causing snow. The letter-writers counted every cycle in their timing loops, just as the author in the story that started this chapter had. Like that author, the letter-writers had failed to take the prefetch queue into account. In fact, they had neglected the effects of video wait states as well, so the code they discussed was actually much slower than their estimates. The proper test would, of course, have been to run the code to see if snow resulted, since the only true measure of code performance is observing it in action.

The Zen Timer

Clearly, one key to mastering Zen-class optimization is a tool with which to measure code performance. The most accurate way to measure performance is with expensive hardware, but reasonable measurements at no cost can be made with the PC’s 8253 timer chip, which counts at a rate of slightly over 1,000,000 times per second. The 8253 can be started at the beginning of a block of code of interest and stopped at the end of that code, with the resulting count indicating how long the code took to execute with an accuracy of about 1 microsecond. (A microsecond is one millionth of a second, and is abbreviated µs). To be precise, the 8253 counts once every 838.1 nanoseconds. (A nanosecond is one billionth of a second, and is abbreviated ns.)

Listing 3.1 shows 8253-based timer software, consisting of three

subroutines: ZTimerOn, ZTimerOff, and

ZTimerReport. For the remainder of this book, I’ll refer to

these routines collectively as the “Zen timer.” C-callable versions of

the two precision Zen timers are presented in Chapter K on the companion

CD-ROM.

LISTING 3.1 PZTIMER.ASM

; The precision Zen timer (PZTIMER.ASM)

;

; Uses the 8253 timer to time the performance of code that takes

; less than about 54 milliseconds to execute, with a resolution

; of better than 10 microseconds.

;

; By Michael Abrash

;

; Externally callable routines:

;

; ZTimerOn: Starts the Zen timer, with interrupts disabled.

;

; ZTimerOff: Stops the Zen timer, saves the timer count,

; times the overhead code, and restores interrupts to the

; state they were in when ZTimerOn was called.

;

; ZTimerReport: Prints the net time that passed between starting

; and stopping the timer.

;

; Note: If longer than about 54 ms passes between ZTimerOn and

; ZTimerOff calls, the timer turns over and the count is

; inaccurate. When this happens, an error message is displayed

; instead of a count. The long-period Zen timer should be used

; in such cases.

;

; Note: Interrupts *MUST* be left off between calls to ZTimerOn

; and ZTimerOff for accurate timing and for detection of

; timer overflow.

;

; Note: These routines can introduce slight inaccuracies into the

; system clock count for each code section timed even if

; timer 0 doesn't overflow. If timer 0 does overflow, the

; system clock can become slow by virtually any amount of

; time, since the system clock can't advance while the

; precison timer is timing. Consequently, it's a good idea

; to reboot at the end of each timing session. (The

; battery-backed clock, if any, is not affected by the Zen

; timer.)

;

; All registers, and all flags except the interrupt flag, are

; preserved by all routines. Interrupts are enabled and then disabled

; by ZTimerOn, and are restored by ZTimerOff to the state they were

; in when ZTimerOn was called.

;

Code segment word public 'CODE'

assume cs:Code, ds:nothing

public ZTimerOn, ZTimerOff, ZTimerReport

;

; Base address of the 8253 timer chip.

;

BASE_8253 equ 40h

;

; The address of the timer 0 count registers in the 8253.

;

TIMER_0_8253 equ BASE_8253 + 0

;

; The address of the mode register in the 8253.

;

MODE_8253 equ BASE_8253 + 3

;

; The address of Operation Command Word 3 in the 8259 Programmable

; Interrupt Controller (PIC) (write only, and writable only when

; bit 4 of the byte written to this address is 0 and bit 3 is 1).

;

OCW3 equ 20h

;

; The address of the Interrupt Request register in the 8259 PIC

; (read only, and readable only when bit 1 of OCW3 = 1 and bit 0

; of OCW3 = 0).

;

IRR equ 20h

;

; Macro to emulate a POPF instruction in order to fix the bug in some

; 80286 chips which allows interrupts to occur during a POPF even when

; interrupts remain disabled.

;

MPOPF macro

local p1, p2

jmp short p2

p1: iret ; jump to pushed address & pop flags

p2: push cs ; construct far return address to

call p1 ; the next instruction

endm

;

; Macro to delay briefly to ensure that enough time has elapsed

; between successive I/O accesses so that the device being accessed

; can respond to both accesses even on a very fast PC.

;

DELAY macro

jmp $+2

jmp $+2

jmp $+2

endm

OriginalFlags db ? ; storage for upper byte of

; FLAGS register when

; ZTimerOn called

TimedCount dw ? ; timer 0 count when the timer

; is stopped

ReferenceCount dw ? ; number of counts required to

; execute timer overhead code

OverflowFlag db ? ; used to indicate whether the

; timer overflowed during the

; timing interval

;

; String printed to report results.

;

OutputStr label byte

db 0dh, 0ah, 'Timed count: ', 5 dup (?)

ASCIICountEnd label byte

db ' microseconds', 0dh, 0ah

db '$'

;

; String printed to report timer overflow.

;

OverflowStr label byte

db 0dh, 0ah

db '****************************************************'

db 0dh, 0ah

db '* The timer overflowed, so the interval timed was *'

db 0dh, 0ah

db '* too long for the precision timer to measure. *'

db 0dh, 0ah

db '* Please perform the timing test again with the *'

db 0dh, 0ah

db '* long-period timer. *'

db 0dh, 0ah

db '****************************************************'

db 0dh, 0ah

db '$'

; ********************************************************************

; * Routine called to start timing. *

; ********************************************************************

ZTimerOn proc near

;

; Save the context of the program being timed.

;

push ax

pushf

pop ax ; get flags so we can keep

; interrupts off when leaving

; this routine

mov cs:[OriginalFlags],ah ; remember the state of the

; Interrupt flag

and ah,0fdh ; set pushed interrupt flag

; to 0

push ax

;

; Turn on interrupts, so the timer interrupt can occur if it's

; pending.

;

sti

;

; Set timer 0 of the 8253 to mode 2 (divide-by-N), to cause

; linear counting rather than count-by-two counting. Also

; leaves the 8253 waiting for the initial timer 0 count to

; be loaded.

;

mov al,00110100b ;mode 2

out MODE_8253,al

;

; Set the timer count to 0, so we know we won't get another

; timer interrupt right away.

; Note: this introduces an inaccuracy of up to 54 ms in the system

; clock count each time it is executed.

;

DELAY

sub al,al

out TIMER_0_8253,al ;lsb

DELAY

out TIMER_0_8253,al ;msb

;

; Wait before clearing interrupts to allow the interrupt generated

; when switching from mode 3 to mode 2 to be recognized. The delay

; must be at least 210 ns long to allow time for that interrupt to

; occur. Here, 10 jumps are used for the delay to ensure that the

; delay time will be more than long enough even on a very fast PC.

;

rept 10

jmp $+2

endm

;

; Disable interrupts to get an accurate count.

;

cli

;

; Set the timer count to 0 again to start the timing interval.

;

mov al,00110100b ; set up to load initial

out MODE_8253,al ; timer count

DELAY

sub al,al

out TIMER_0_8253,al ; load count lsb

DELAY

out TIMER_0_8253,al; load count msb

;

; Restore the context and return.

;

MPOPF ; keeps interrupts off

pop ax

ret

ZTimerOn endp

;********************************************************************

;* Routine called to stop timing and get count. *

;********************************************************************

ZTimerOff proc near

;

; Save the context of the program being timed.

;

push ax

push cx

pushf

;

; Latch the count.

;

mov al,00000000b ; latch timer 0

out MODE_8253,al

;

; See if the timer has overflowed by checking the 8259 for a pending

; timer interrupt.

;

mov al,00001010b ; OCW3, set up to read

out OCW3,al ; Interrupt Request register

DELAY

in al,IRR ; read Interrupt Request

; register

and al,1 ; set AL to 1 if IRQ0 (the

; timer interrupt) is pending

mov cs:[OverflowFlag],al; store the timer overflow

; status

;

; Allow interrupts to happen again.

;

sti

;

; Read out the count we latched earlier.

;

in al,TIMER_0_8253 ; least significant byte

DELAY

mov ah,al

in al,TIMER_0_8253 ; most significant byte

xchg ah,al

neg ax ; convert from countdown

; remaining to elapsed

; count

mov cs:[TimedCount],ax

; Time a zero-length code fragment, to get a reference for how

; much overhead this routine has. Time it 16 times and average it,

; for accuracy, rounding the result.

;

mov cs:[ReferenceCount],0

mov cx,16

cli ; interrupts off to allow a

; precise reference count

RefLoop:

call ReferenceZTimerOn

call ReferenceZTimerOff

loop RefLoop

sti

add cs:[ReferenceCount],8; total + (0.5 * 16)

mov cl,4

shr cs:[ReferenceCount],cl; (total) / 16 + 0.5

;

; Restore original interrupt state.

;

pop ax ; retrieve flags when called

mov ch,cs:[OriginalFlags] ; get back the original upper

; byte of the FLAGS register

and ch,not 0fdh ; only care about original

; interrupt flag...

and ah,0fdh ; ...keep all other flags in

; their current condition

or ah,ch ; make flags word with original

; interrupt flag

push ax ; prepare flags to be popped

;

; Restore the context of the program being timed and return to it.

;

MPOPF ; restore the flags with the

; original interrupt state

pop cx

pop ax

ret

ZTimerOff endp

;

; Called by ZTimerOff to start timer for overhead measurements.

;

ReferenceZTimerOn proc near

;

; Save the context of the program being timed.

;

push ax

pushf ; interrupts are already off

;

; Set timer 0 of the 8253 to mode 2 (divide-by-N), to cause

; linear counting rather than count-by-two counting.

;

mov al,00110100b ; set up to load

out MODE_8253,al ; initial timer count

DELAY

;

; Set the timer count to 0.

;

sub al,al

out TIMER_0_8253,al; load count lsb

DELAY

out TIMER_0_8253,al; load count msb

;

; Restore the context of the program being timed and return to it.

;

MPOPF

pop ax

ret

ReferenceZTimerOn endp

;

; Called by ZTimerOff to stop timer and add result to ReferenceCount

; for overhead measurements.

;

ReferenceZTimerOff proc near

;

; Save the context of the program being timed.

;

push ax

push cx

pushf

;

; Latch the count and read it.

;

mov al,00000000b ; latch timer 0

out MODE_8253,al

DELAY

in al,TIMER_0_8253 ; lsb

DELAY

mov ah,al

in al,TIMER_0_8253 ; msb

xchg ah,al

neg ax ; convert from countdown

; remaining to amount

; counted down

add cs:[ReferenceCount],ax

;

; Restore the context of the program being timed and return to it.

;

MPOPF

pop cx

pop ax

ret

ReferenceZTimerOff endp

; ********************************************************************

; * Routine called to report timing results. *

; ********************************************************************

ZTimerReport proc near

pushf

push ax

push bx

push cx

push dx

push si

push ds

;

push cs ; DOS functions require that DS point

pop ds ; to text to be displayed on the screen

assume ds :Code

;

; Check for timer 0 overflow.

;

cmp [OverflowFlag],0

jz PrintGoodCount

mov dx,offset OverflowStr

mov ah,9

int 21h

jmp short EndZTimerReport

;

; Convert net count to decimal ASCII in microseconds.

;

PrintGoodCount:

mov ax,[TimedCount]

sub ax,[ReferenceCount]

mov si,offset ASCIICountEnd - 1

;

; Convert count to microseconds by multiplying by .8381.

;

mov dx, 8381

mul dx

mov bx, 10000

div bx ;* .8381 = * 8381 / 10000

;

; Convert time in microseconds to 5 decimal ASCII digits.

;

mov bx, 10

mov cx, 5

CTSLoop:

sub dx, dx

div bx

add dl,'0'

mov [si],dl

dec si

loop CTSLoop

;

; Print the results.

;

mov ah, 9

mov dx, offset OutputStr

int 21h

;

EndZTimerReport:

pop ds

pop si

pop dx

pop cx

pop bx

pop ax

MPOPF

ret

ZTimerReport endp

Code ends

endThe Zen Timer Is a Means, Not an End

We’re going to spend the rest of this chapter seeing what the Zen timer can do, examining how it works, and learning how to use it. I’ll be using the Zen timer again and again over the course of this book, so it’s essential that you learn what the Zen timer can do and how to use it. On the other hand, it is by no means essential that you understand exactly how the Zen timer works. (Interesting, yes; essential, no.)

In other words, the Zen timer isn’t really part of the knowledge we seek; rather, it’s one tool with which we’ll acquire that knowledge. Consequently, you shouldn’t worry if you don’t fully grasp the inner workings of the Zen timer. Instead, focus on learning how to use it, and you’ll be on the right road.

Starting the Zen Timer

ZTimerOn is called at the start of a segment of code to

be timed. ZTimerOn saves the context of the calling code,

disables interrupts, sets timer 0 of the 8253 to mode 2 (divide-by-N

mode), sets the initial timer count to 0, restores the context of the

calling code, and returns. (I’d like to note that while Intel’s

documentation for the 8253 seems to indicate that a timer won’t reset to

0 until it finishes counting down, in actual practice, timers seem to

reset to 0 as soon as they’re loaded.)

Two aspects of ZTimerOn are worth discussing further.

One point of interest is that ZTimerOn disables interrupts.

(ZTimerOff later restores interrupts to the state they were

in when ZTimerOn was called.) Were interrupts not disabled

by ZTimerOn, keyboard, mouse, timer, and other interrupts

could occur during the timing interval, and the time required to service

those interrupts would incorrectly and erratically appear to be part of

the execution time of the code being measured. As a result, code timed

with the Zen timer should not expect any hardware interrupts to occur

during the interval between any call to ZTimerOn and the

corresponding call to ZTimerOff, and should not enable

interrupts during that time.

Time and the PC

A second interesting point about ZTimerOn is that it may

introduce some small inaccuracy into the system clock time whenever it

is called. To understand why this is so, we need to examine the way in

which both the 8253 and the PC’s system clock (which keeps the current

time) work.

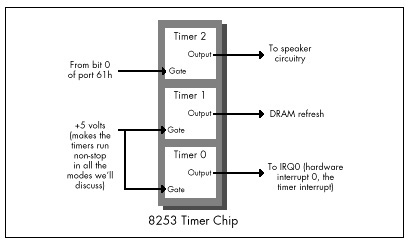

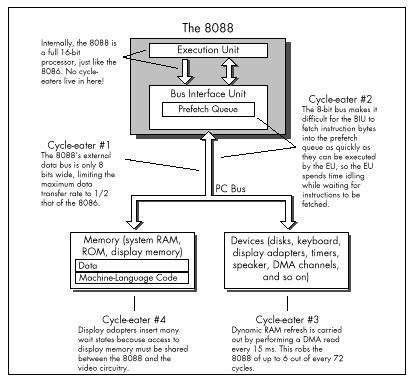

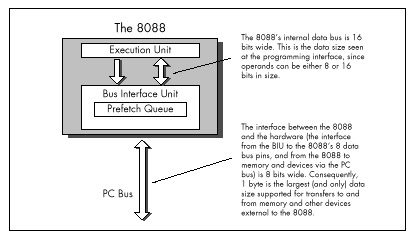

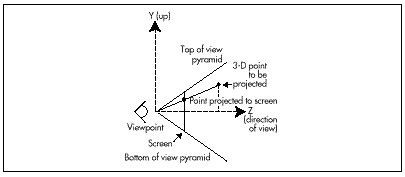

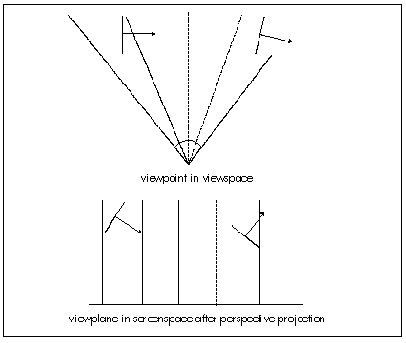

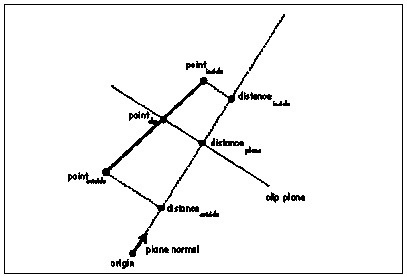

The 8253 actually contains three timers, as shown in Figure 3.1. All three timers are driven by the system board’s 14.31818 MHz crystal, divided by 12 to yield a 1.19318 MHz clock to the timers, so the timers count once every 838.1 ns. Each of the three timers counts down in a programmable way, generating a signal on its output pin when it counts down to 0. Each timer is capable of being halted at any time via a 0 level on its gate input; when a timer’s gate input is 1, that timer counts constantly. All in all, the 8253’s timers are inherently very flexible timing devices; unfortunately, much of that flexibility depends on how the timers are connected to external circuitry, and in the PC the timers are connected with specific purposes in mind.

Timer 2 drives the speaker, although it can be used for other timing purposes when the speaker is not in use. As shown in Figure 3.1, timer 2 is the only timer with a programmable gate input in the PC; that is, timer 2 is the only timer that can be started and stopped under program control in the manner specified by Intel. On the other hand, the output of timer 2 is connected to nothing other than the speaker. In particular, timer 2 cannot generate an interrupt to get the 8088’s attention.

Timer 1 is dedicated to providing dynamic RAM refresh, and should not be tampered with lest system crashes result.

Finally, timer 0 is used to drive the system clock. As programmed by the BIOS at power-up, every 65,536 (64K) counts, or 54.925 milliseconds, timer 0 generates a rising edge on its output line. (A millisecond is one-thousandth of a second, and is abbreviated ms.) This line is connected to the hardware interrupt 0 (IRQ0) line on the system board, so every 54.925 ms, timer 0 causes hardware interrupt 0 to occur.

The interrupt vector for IRQ0 is set by the BIOS at power-up time to

point to a BIOS routine, TIMER_INT, that maintains a

time-of-day count. TIMER_INT keeps a 16-bit count of IRQ0

interrupts in the BIOS data area at address 0000:046C (all addresses in

this book are given in segment:offset hexadecimal pairs); this count

turns over once an hour (less a few microseconds), and when it does,

TIMER_INT updates a 16-bit hour count at address 0000:046E

in the BIOS data area. This count is the basis for the current time and

date that DOS supports via functions 2AH (2A hexadecimal) through 2DH

and by way of the DATE and TIME commands.

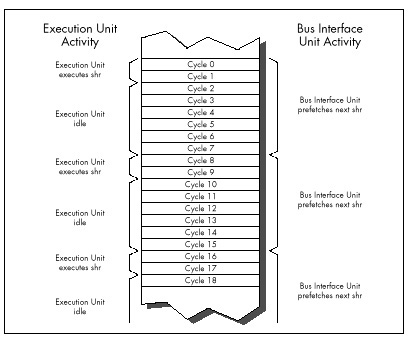

Each timer channel of the 8253 can operate in any of six modes. Timer 0 normally operates in mode 3: square wave mode. In square wave mode, the initial count is counted down two at a time; when the count reaches zero, the output state is changed. The initial count is again counted down two at a time, and the output state is toggled back when the count reaches zero. The result is a square wave that changes state more slowly than the input clock by a factor of the initial count. In its normal mode of operation, timer 0 generates an output pulse that is low for about 27.5 ms and high for about 27.5 ms; this pulse is sent to the 8259 interrupt controller, and its rising edge generates a timer interrupt once every 54.925 ms.

Square wave mode is not very useful for precision timing because it counts down by two twice per timer interrupt, thereby rendering exact timings impossible. Fortunately, the 8253 offers another timer mode, mode 2 (divide-by-N mode), which is both a good substitute for square wave mode and a perfect mode for precision timing.

Divide-by-N mode counts down by one from the initial count. When the count reaches zero, the timer turns over and starts counting down again without stopping, and a pulse is generated for a single clock period. While the pulse is not held for nearly as long as in square wave mode, it doesn’t matter, since the 8259 interrupt controller is configured in the PC to be edge-triggered and hence cares only about the existence of a pulse from timer 0, not the duration of the pulse. As a result, timer 0 continues to generate timer interrupts in divide-by-N mode, and the system clock continues to maintain good time.

Why not use timer 2 instead of timer 0 for precision timing? After all, timer 2 has a programmable gate input and isn’t used for anything but sound generation. The problem with timer 2 is that its output can’t generate an interrupt; in fact, timer 2 can’t do anything but drive the speaker. We need the interrupt generated by the output of timer 0 to tell us when the count has overflowed, and we will see shortly that the timer interrupt also makes it possible to time much longer periods than the Zen timer shown in Listing 3.1 supports.

In fact, the Zen timer shown in Listing 3.1 can only time intervals of up to about 54 ms in length, since that is the period of time that can be measured by timer 0 before its count turns over and repeats. Fifty-four ms may not seem like a very long time, but even a CPU as slow as the 8088 can perform more than 1,000 divides in 54 ms, and division is the single instruction that the 8088 performs most slowly. If a measured period turns out to be longer than 54 ms (that is, if timer 0 has counted down and turned over), the Zen timer will display a message to that effect. A long-period Zen timer for use in such cases will be presented later in this chapter.

The Zen timer determines whether timer 0 has turned over by checking

to see whether an IRQ0 interrupt is pending. (Remember, interrupts are

off while the Zen timer runs, so the timer interrupt cannot be

recognized until the Zen timer stops and enables interrupts.) If an IRQ0

interrupt is pending, then timer 0 has turned over and generated a timer

interrupt. Recall that ZTimerOn initially sets timer 0 to

0, in order to allow for the longest possible period—about 54 ms—before

timer 0 reaches 0 and generates the timer interrupt.

Now we’re ready to look at the ways in which the Zen timer can

introduce inaccuracy into the system clock. Since timer 0 is initially

set to 0 by the Zen timer, and since the system clock ticks only when

timer 0 counts off 54.925 ms and reaches 0 again, an average inaccuracy

of one-half of 54.925 ms, or about 27.5 ms, is incurred each time the

Zen timer is started. In addition, a timer interrupt is generated when

timer 0 is switched from mode 3 to mode 2, advancing the system clock by

up to 54.925 ms, although this only happens the first time the Zen timer

is run after a warm or cold boot. Finally, up to 54.925 ms can again be

lost when ZTimerOff is called, since that routine again

sets the timer count to zero. Net result: The system clock will run up

to 110 ms (about a ninth of a second) slow each time the Zen timer is

used.

Potentially far greater inaccuracy can be incurred by timing code that takes longer than about 110 ms to execute. Recall that all interrupts, including the timer interrupt, are disabled while timing code with the Zen timer. The 8259 interrupt controller is capable of remembering at most one pending timer interrupt, so all timer interrupts after the first one during any given Zen timing interval are ignored. Consequently, if a timing interval exceeds 54.9 ms, the system clock effectively stops 54.9 ms after the timing interval starts and doesn’t restart until the timing interval ends, losing time all the while.

The effects on the system time of the Zen timer aren’t a matter for great concern, as they are temporary, lasting only until the next warm or cold boot. System that have battery-backed clocks, (AT-style machines; that is, virtually all machines in common use) automatically reset the correct time whenever the computer is booted, and systems without battery-backed clocks prompt for the correct date and time when booted. Also, repeated use of the Zen timer usually makes the system clock slow by at most a total of a few seconds, unless code that takes much longer than 54 ms to run is timed (in which case the Zen timer will notify you that the code is too long to time).

Nonetheless, it’s a good idea to reboot your computer at the end of each session with the Zen timer in order to make sure that the system clock is correct.

Stopping the Zen Timer

At some point after ZTimerOn is called,

ZTimerOff must always be called to mark the end of the

timing interval. ZTimerOff saves the context of the calling

program, latches and reads the timer 0 count, converts that count from

the countdown value that the timer maintains to the number of counts

elapsed since ZTimerOn was called, and stores the result.

Immediately after latching the timer 0 count—and before enabling

interrupts—ZTimerOff checks the 8259 interrupt controller

to see if there is a pending timer interrupt, setting a flag to mark

that the timer overflowed if there is indeed a pending timer

interrupt.

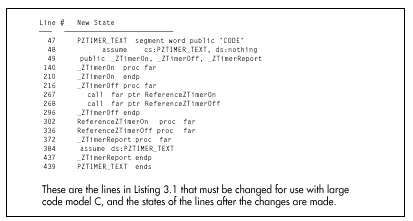

After that, ZTimerOff executes just the overhead code of